# **General Description**

The MAX1180 is a +3.3V, dual 10-bit, analog-to-digital converter (ADC) featuring fully-differential wideband track-and-hold (T/H) inputs, driving two pipelined, ninestage ADCs. The MAX1180 is optimized for low-power, high-dynamic performance applications in imaging, instrumentation, and digital communication applications. The MAX1180 operates from a single +2.7V to +3.6V supply, consuming only 413mW, while delivering a typical signal-to-noise ratio (SNR) of 58.5dB at an input frequency of 20MHz and a sampling rate of 105Msps. The T/H driven input stages incorporate 400MHz (-3dB) input amplifiers. The converters may also be operated with single-ended inputs. In addition to low operating power, the MAX1180 features a 2.8mA sleep mode, as well as a 1µA power-down mode to conserve power during idle periods.

An internal +2.048V precision bandgap reference sets the full-scale range of the ADC. A flexible reference structure allows the use of the internal or external reference, if desired for applications requiring increased accuracy or a different input voltage range.

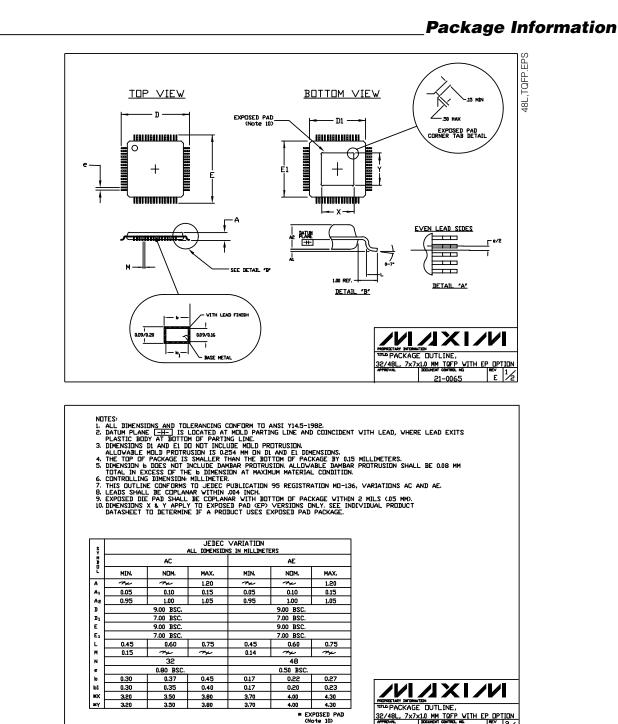

The MAX1180 features parallel, CMOS-compatible three-state outputs. The digital output format is set to two's complement or straight offset binary through a single control pin. The device provides for a separate output power supply of  $\pm 1.7V$  to  $\pm 3.6V$  for flexible interfacing. The MAX1180 is available in a 7mm  $\times$  7mm, 48-pin TQFP package, and is specified for the extended industrial (-40°C to  $\pm 85^{\circ}$ C) temperature range.

Pin-compatible higher and lower speed versions of the MAX1180 are also available. Please refer to the MAX1181 data sheet for 80Msps, the MAX1182 data sheet for 65Msps, the MAX1183 data sheet for 40Msps, and the MAX1184 data sheet for 20Msps. In addition to these speed grades, this family includes a 20Msps multiplexed output version (MAX1185), for which digital data is presented time-interleaved on a single, parallel 10-bit output port.

# Applications

- High Resolution Imaging

- I/Q Channel Digitization

- Multichannel IF Undersampling

- Instrumentation

- Video Application

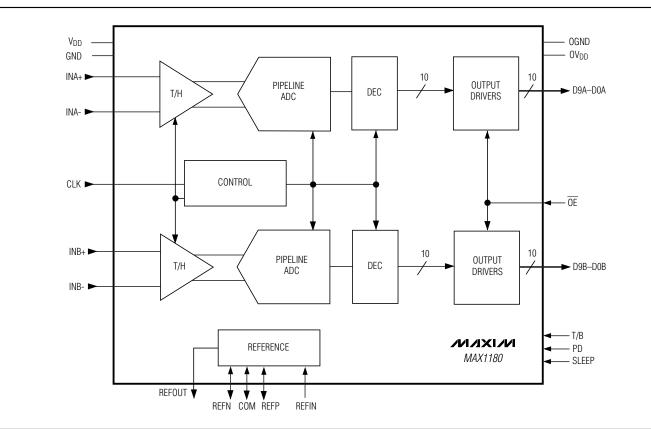

Functional Diagram appears at end of data sheet.

# **Features**

- Single +3.3V Operation

- Excellent Dynamic Performance: 58.5dB SNR at f<sub>IN</sub> = 20MHz 72dB SFDR at f<sub>IN</sub> = 20MHz

- SNR Flat within 1dB for fIN = 202MHz to 100MHz

M/XI/M

- Low Power: 125mA (Normal Operation) 2.8mA (Sleep Mode) 1µA (Shutdown Mode)

- 0.02dB Gain and 0.25° Phase Matching (typ)

- Wide ±1Vp-p Differential Analog Input Voltage Range

- ♦ 400MHz, -3dB Input Bandwidth

- On-Chip +2.048V Precision Bandgap Reference

- User-Selectable Output Format—Two's Complement or Offset Binary

- 48-Pin TQFP Package with Exposed Pad for Improved Thermal Dissipation

# Ordering Information

| PART |         | TEMP. RANGE    | PIN-PACKAGE |

|------|---------|----------------|-------------|

| MAX  | 1180ECM | -40°C to +85°C | 48 TQFP-EP  |

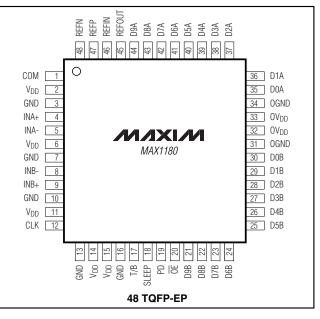

# Pin Configuration

Maxim Integrated Products 1

MIXI/M

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> , OV <sub>DD</sub> to GND<br>OGND to GND |                                   |

|----------------------------------------------------------|-----------------------------------|

| INA+, INA-, INB+, INB- to GND                            |                                   |

| REFIN, REFOUT, REFP, REFN, CLK,<br>COM to GND            | -0.3V to (Vpp + 0.3V)             |

| OE, PD, SLEEP, T/B, D9A–D0A,                             |                                   |

| D9B–D0B to OGND                                          | 0.3V to (OV <sub>DD</sub> + 0.3V) |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

|-------------------------------------------------------|---------------|

| 48-Pin TQFP (derate 12.5mW/°C above +70               | °C)1000mW     |

| Operating Temperature Range                           | 40°C to +85°C |

| Junction Temperature                                  | +150°C        |

| Storage Temperature Range                             |               |

| Lead Temperature (soldering, 10s)                     | +300°C        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +3.3V, OV_{DD} = +2.5V; 0.1\mu$ F and  $1.0\mu$ F capacitors from REFP, REFN, and COM to GND; REFOUT connected to REFIN through a 10k $\Omega$  resistor,  $V_{IN} = 2V_{p-p}$  (differential w.r.t. COM),  $C_L = 10$ pF at digital outputs (Note 5),  $f_{CLK} = 105.263$ MHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.)

| PARAMETER                                                       | SYMBOL                    | CONDITIONS                                                                 | MIN  | ТҮР                         | MAX  | UNITS           |  |

|-----------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------|------|-----------------------------|------|-----------------|--|

| DC ACCURACY                                                     | •                         |                                                                            |      |                             |      | •               |  |

| Resolution                                                      |                           |                                                                            | 10   |                             |      | Bits            |  |

| Integral Nonlinearity                                           | INL                       | $f_{IN} = 7.47 MHz$                                                        |      | ±0.75                       | ±2.5 | LSB             |  |

| Differential Nonlinearity                                       | DNL                       | f <sub>IN</sub> = 7.47MHz, no missing codes guaranteed                     | -1   | ±0.4                        | +1.5 | LSB             |  |

| Offset Error                                                    |                           |                                                                            |      | < ±1                        | ±1.7 | % FS            |  |

| Gain Error                                                      |                           |                                                                            |      | 0                           | ±2   | % FS            |  |

| ANALOG INPUT                                                    |                           |                                                                            |      |                             |      |                 |  |

| Differential Input Voltage Range                                | VDIFF                     | Differential or single-ended inputs                                        |      | ±1.0                        |      | V               |  |

| Common-Mode Input Voltage<br>Range                              | VCM                       |                                                                            |      | V <sub>DD</sub> /2<br>± 0.5 |      | V               |  |

| Input Resistance                                                | R <sub>IN</sub>           | Switched capacitor load                                                    |      | 20                          |      | kΩ              |  |

| Input Capacitance                                               | CIN                       |                                                                            |      | 5                           |      | pF              |  |

| CONVERSION RATE                                                 |                           |                                                                            |      |                             |      |                 |  |

| Maximum Clock Frequency                                         | fCLK                      |                                                                            | 105  |                             |      | MHz             |  |

| Data Latency                                                    |                           |                                                                            |      | 5                           |      | Clock<br>Cycles |  |

| DYNAMIC CHARACTERISTICS                                         | (f <sub>CLK</sub> = 105.2 | 263MHz, 4096-point FFT)                                                    |      |                             |      |                 |  |

|                                                                 |                           | $f_{INA \text{ or } B} = 7.47 \text{MHz}, T_A = +25^{\circ}\text{C}$       |      | 59                          |      |                 |  |

| Signal-to-Noise Ratio                                           | SNR                       | $f_{INA \text{ or } B} = 20 \text{MHz}, T_A = +25^{\circ}\text{C}$         | 55   | 58.5                        |      | dB              |  |

|                                                                 |                           | f <sub>INA or B</sub> = 50.078MHz (Note 1)                                 |      | 58                          |      |                 |  |

|                                                                 |                           | $f_{INA \text{ or } B} = 7.47 \text{MHz}, T_A = +25^{\circ}\text{C}$       |      | 58.2                        |      |                 |  |

| Signal-to-Noise and Distortion (up to 5 <sup>th</sup> harmonic) | SINAD                     | $f_{INA \text{ or } B} = 20 \text{MHz}, T_A = +25^{\circ}\text{C}$         | 54.7 | 54.7 58.1                   |      | dB              |  |

| (up to 3 marmonic)                                              |                           | f <sub>INA or B</sub> = 50.078MHz (Note 1)                                 |      | 57.6                        |      | 1               |  |

|                                                                 |                           | $f_{INA \text{ or } B} = 7.47 \text{MHz}, T_A = +25^{\circ}\text{C}$       |      | 72                          |      |                 |  |

| Spurious-Free Dynamic<br>Range                                  | SFDR                      | SFDR $f_{INA \text{ or } B} = 20 \text{MHz}, T_A = +25^{\circ}\text{C}$ 60 |      | 72                          |      | dBc             |  |

|                                                                 |                           | f <sub>INA or B</sub> = 50.078MHz, (Note 1)                                |      | 70                          |      |                 |  |

|                                                                 |                           | $f_{INA \text{ or } B} = 7.47 \text{MHz}$                                  |      | -75                         |      |                 |  |

| Third-Harmonic Distortion                                       | HD3                       | fINA or B = 20MHz                                                          |      | -75                         | dBc  |                 |  |

|                                                                 |                           | f <sub>INA or B</sub> = 50.078MHz (Note 1)                                 |      | -73                         |      |                 |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.3V, OV_{DD} = +2.5V; 0.1\mu$ F and  $1.0\mu$ F capacitors from REFP, REFN, and COM to GND; REFOUT connected to REFIN through a 10k $\Omega$  resistor,  $V_{IN} = 2V_{p-p}$  (differential w.r.t. COM),  $C_L = 10$ pF at digital outputs (Note 5),  $f_{CLK} = 105.263$ MHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.)

| PARAMETER                                                 | SYMBOL             | CONDITIONS                                                                                                                                                         | MIN  | ТҮР          | MAX  | UNITS              |

|-----------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|------|--------------------|

| Intermodulation Distortion<br>(first five odd-order IMDs) | IMD                | $f_{INA \text{ or } B} = 38.055 \text{MHz} \text{ at } -6.5 \text{dB FS}$<br>$f_{INA \text{ or } B} = 42.926 \text{MHz} \text{ at } -6.5 \text{dB FS}$<br>(Note 2) |      | -74          |      | dBc                |

| Total Llargencia Distortion                               |                    | $f_{INA \text{ or } B} = 7.47 \text{MHz}, T_A = +25^{\circ}\text{C}$                                                                                               |      | -71          |      |                    |

| Total Harmonic Distortion<br>(first five harmonics)       | THD                | $f_{INA \text{ or } B} = 20 \text{MHz}, T_A = +25^{\circ}\text{C}$                                                                                                 |      | -70          | -59  | dBc                |

|                                                           |                    | f <sub>INA or B</sub> = 50.078MHz, (Note 1)                                                                                                                        |      | -69          |      |                    |

| Small-Signal Bandwidth                                    |                    | Input at -20dB FS, differential inputs                                                                                                                             |      | 500          |      | MHz                |

| Full-Power Bandwidth                                      | FPBW               | Input at -0.5dB FS, differential inputs                                                                                                                            |      | 400          |      | MHz                |

| Aperture Delay                                            | tad                |                                                                                                                                                                    |      | 1            |      | ns                 |

| Aperture Jitter                                           | taj                |                                                                                                                                                                    |      | 2            |      | ps <sub>RMS</sub>  |

| Overdrive Recovery Time                                   |                    | For 1.5 × full-scale input                                                                                                                                         |      | 2            |      | ns                 |

| Differential Gain                                         |                    |                                                                                                                                                                    |      | ±1           |      | %                  |

| Differential Phase                                        |                    |                                                                                                                                                                    |      | ±0.25        |      | degrees            |

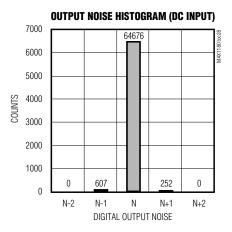

| Output Noise                                              |                    | INA+ = INA- = INB+ = INB- = COM                                                                                                                                    |      | 0.2          |      | LSB <sub>RMS</sub> |

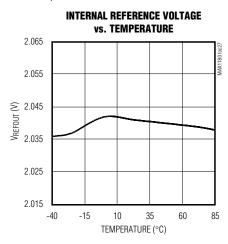

| INTERNAL REFERENCE                                        |                    |                                                                                                                                                                    | ·    |              |      |                    |

| Reference Output Voltage                                  | REFOUT             |                                                                                                                                                                    |      | 2.048<br>±3% |      | V                  |

| Reference Temperature<br>Coefficient                      | TC <sub>REF</sub>  |                                                                                                                                                                    |      | 60           |      | ppm/°C             |

| Load Regulation                                           |                    |                                                                                                                                                                    |      | 1.25         |      | mV/mA              |

| <b>BUFFERED EXTERNAL REFERI</b>                           | ENCE (VREFI        | N = +2.048V)                                                                                                                                                       |      |              |      |                    |

| REFIN Input Voltage                                       | VREFIN             |                                                                                                                                                                    |      | 2.048        |      | V                  |

| Positive Reference Output<br>Voltage                      | V <sub>REFP</sub>  |                                                                                                                                                                    |      | 2.162        |      | V                  |

| Negative Reference Output<br>Voltage                      | V <sub>REFN</sub>  |                                                                                                                                                                    |      | 1.138        |      | V                  |

| Differential Reference Output<br>Voltage Range            | $\Delta V_{REF}$   | $\Delta V_{REF} = V_{REFP} - V_{REFN}$                                                                                                                             | 0.98 | 1.024        | 1.07 | V                  |

| REFIN Resistance                                          | R <sub>REFIN</sub> |                                                                                                                                                                    |      | >50          |      | MΩ                 |

| Maximum REFP, COM Source<br>Current                       | ISOURCE            |                                                                                                                                                                    |      | 5            |      | mA                 |

| Maximum REFP, COM Sink<br>Current                         | ISINK              |                                                                                                                                                                    |      | -250         |      | μA                 |

| Maximum REFN Source Current                               | ISOURCE            |                                                                                                                                                                    |      | 250          |      | μA                 |

| Maximum REFN Sink Current                                 | Isink              |                                                                                                                                                                    |      | -5           |      | mA                 |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.3V, OV_{DD} = +2.5V; 0.1\mu$ F and  $1.0\mu$ F capacitors from REFP, REFN, and COM to GND; REFOUT connected to REFIN through a 10k $\Omega$  resistor,  $V_{IN} = 2V_{p-p}$  (differential w.r.t. COM),  $C_L = 10$ pF at digital outputs (Note 5),  $f_{CLK} = 105.263$ MHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.)

| PARAMETER                                     | SYMBOL            | CONDITIONS                                                      | MIN                       | ТҮР                                | MAX                       | UNITS |

|-----------------------------------------------|-------------------|-----------------------------------------------------------------|---------------------------|------------------------------------|---------------------------|-------|

| UNBUFFERED EXTERNAL REFI                      | ERENCE (VR        | REFIN = AGND, reference voltage applied to REF                  | P, REFN,                  | and COM                            | )                         |       |

| REFP, REFN Input Resistance                   | Rrefp,<br>Rrefn   | Measured between REFP and COM and REFN and COM                  |                           | 4                                  |                           | kΩ    |

| Differential Reference Input<br>Voltage Range | $\Delta V_{REF}$  | $\Delta V_{REF} = V_{REFP} - V_{REFN}$                          |                           | 1.024<br>±10%                      |                           | V     |

| COM Input Voltage Range                       | V <sub>COM</sub>  |                                                                 |                           | V <sub>DD</sub> /2<br>±10%         |                           | V     |

| REFP Input Voltage                            | V <sub>REFP</sub> |                                                                 |                           | $V_{COM}$ +<br>$\Delta V_{REF}$ /2 |                           | V     |

| REFN Input Voltage                            | VREFN             |                                                                 |                           | $V_{COM}$ - $\Delta V_{REF}$ /2    |                           | V     |

| DIGITAL INPUTS (CLK, PD, OE,                  | SLEEP, T/B        | 3)                                                              |                           |                                    |                           |       |

| Input Ligh Threshold                          | Maria             | CLK                                                             | 0.8 x<br>V <sub>DD</sub>  |                                    |                           | v     |

| Input High Threshold                          | ViH               | PD, OE, SLEEP, T/B                                              | 0.8 x<br>OV <sub>DD</sub> |                                    |                           | V     |

| land the Three heads                          | VIL               | CLK                                                             |                           |                                    | 0.2 x<br>V <sub>DD</sub>  |       |

| Input Low Threshold                           |                   | PD, OE, SLEEP, T/B                                              |                           |                                    | 0.2 x<br>OV <sub>DD</sub> | V     |

| Input Hysteresis                              | V <sub>HYST</sub> |                                                                 |                           | 0.1                                |                           | V     |

| Input Leakage                                 | Iн                | $V_{IH} = OV_{DD} \text{ or } V_{DD} (CLK)$                     |                           |                                    | ±5                        |       |

| Input Leakage                                 | Ι <sub>ΙL</sub>   | $V_{IL} = 0$                                                    |                           |                                    | ±5                        | μA    |

| Input Capacitance                             | CIN               |                                                                 |                           | 5                                  |                           | pF    |

| DIGITAL OUTPUTS (D9A-D0A, I                   | 09B-D0B)          |                                                                 |                           |                                    |                           |       |

| Output Voltage Low                            | VOL               | I <sub>SINK</sub> = -200μΑ                                      |                           |                                    | 0.2                       | V     |

| Output Voltage High                           | V <sub>OH</sub>   | ISOURCE = 200µA                                                 | OV <sub>DD</sub><br>- 0.2 |                                    |                           | V     |

| Three-State Leakage Current                   | ILEAK             | $\overline{OE} = OV_{DD}$                                       |                           |                                    | ±10                       | μA    |

| Three-State Output Capacitance                | COUT              | $\overline{OE} = OV_{DD}$                                       |                           | 5                                  |                           | pF    |

| POWER REQUIREMENTS                            |                   |                                                                 |                           |                                    |                           |       |

| Analog Supply Voltage Range                   | V <sub>DD</sub>   |                                                                 | 2.7                       | 3.3                                | 3.6                       | V     |

| Output Supply Voltage Range                   | OV <sub>DD</sub>  |                                                                 | 1.7                       | 2.5                                | 3.6                       | V     |

|                                               |                   | Operating, $f_{INA \text{ or } B} = 20 \text{MHz}$ at -0.5dB FS |                           | 125                                | 155                       | mA    |

| Analog Supply Current                         | IVDD              | Sleep mode                                                      |                           | 2.8                                |                           |       |

|                                               |                   | Shutdown, clock idle, PD = $\overline{OE}$ = $OV_{DD}$          |                           | 1                                  | 15                        | μΑ    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.3V, OV_{DD} = +2.5V; 0.1\mu F and 1.0\mu F capacitors from REFP, REFN, and COM to GND; REFOUT connected to REFIN through a 10k<math>\Omega$  resistor,  $V_{IN} = 2V_{p-p}$  (differential w.r.t. COM),  $C_L = 10pF$  at digital outputs (Note 5),  $f_{CLK} = 105.263MHz$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                     | SYMBOL           | CONDITIONS                                                                      | MIN | ТҮР          | MAX  | UNITS   |  |

|-------------------------------|------------------|---------------------------------------------------------------------------------|-----|--------------|------|---------|--|

| Output Querely Querent        | 1                | Operating, C <sub>L</sub> = 15pF , $f_{INA \text{ or } B}$ = 20MHz at -0.5dB FS |     | 15           |      | mA      |  |

| Output Supply Current         | IOVDD            | Sleep mode                                                                      |     | 100          |      | μΑ      |  |

|                               |                  | Shutdown, clock idle, PD = $\overline{OE}$ = $OV_{DD}$                          |     | 2            | 10   | μA      |  |

|                               |                  | Operating, f <sub>INA or B</sub> = 20MHz at -0.5dB FS                           |     | 413          | 511  | mW      |  |

| Power Dissipation             | PDISS            | Sleep mode                                                                      |     | 9.2          |      |         |  |

|                               |                  | Shutdown, clock idle, PD = $\overline{OE}$ = $OV_{DD}$                          |     | 3            | 50   | μW      |  |

| Power Supply Paination Patio  | PSRR             | Offset                                                                          |     | ±0.2         |      | mV/V    |  |

| Power-Supply Rejection Ratio  | FORR             | Gain                                                                            |     | ±0.1         |      | %/V     |  |

| TIMING CHARACTERISTICS        |                  |                                                                                 |     |              |      |         |  |

| CLK Rise to Output Data Valid | tDO              | Figure 3 (Note 3)                                                               |     | 5            | 8    | ns      |  |

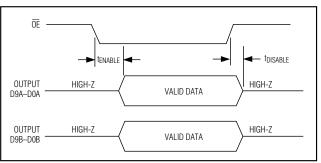

| Output Enable Time            | <b>t</b> ENABLE  | Figure 4                                                                        |     | 10           |      | ns      |  |

| Output Disable Time           | <b>t</b> DISABLE | Figure 4                                                                        |     | 1.5          |      | ns      |  |

| CLK Pulse Width High          | tСН              | Figure 3, clock period: 9.5ns                                                   |     | 4.75<br>±1.5 |      | ns      |  |

| CLK Pulse Width Low           | tCL              | Figure 3, clock period: 9.5ns                                                   |     | 4.75<br>±1.5 |      | ns      |  |

|                               |                  | Wakeup from sleep mode (Note 4)                                                 |     | 0.18         |      |         |  |

| Wake-Up Time                  | twake            | Wakeup from shutdown (Note 4)                                                   |     | 1.5          |      | μs      |  |

| CHANNEL-TO-CHANNEL MATCH      | IING             |                                                                                 |     |              |      |         |  |

| Crosstalk                     |                  | f <sub>INA or B</sub> = 20MHz at -0.5dB FS                                      |     | -70          |      | dB      |  |

| Gain Matching                 |                  | f <sub>INA or B</sub> = 20MHz at -0.5dB FS                                      |     | 0.02         | ±0.2 | dB      |  |

| Phase Matching                |                  | $f_{INA \text{ or } B} = 20 \text{MHz} \text{ at } -0.5 \text{dB FS}$           |     | 0.25         |      | degrees |  |

Note 1: SNR, SINAD, THD, SFDR, and HD3 are based on an analog input voltage of -0.5dB FS, referenced to a +1.024V full-scale input voltage range.

**Note 2:** Intermodulation distortion is the total power of the intermodulation products relative to the individual carrier. This number is 6dB or better, if referenced to the two-tone envelope.

Note 3: Digital outputs settle to  $V_{IH}$ ,  $V_{IL}$ . Parameter guaranteed by design.

Note 4: With REFIN driven externally, REFP, COM, and REFN are left floating while powered down.

Note 5: Equivalent dynamic performance is obtainable over full OV<sub>DD</sub> range with reduced CL.

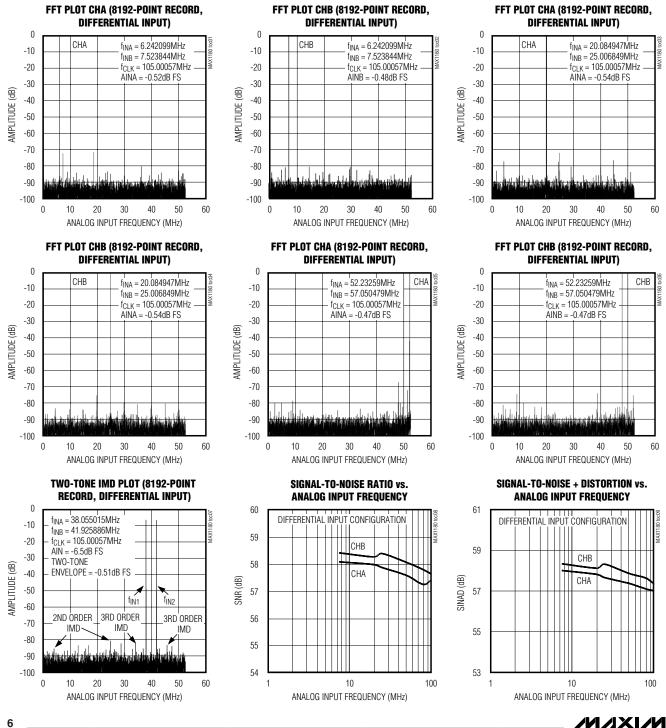

Typical Operating Characteristics

MAX1180

unless otherwise noted.)

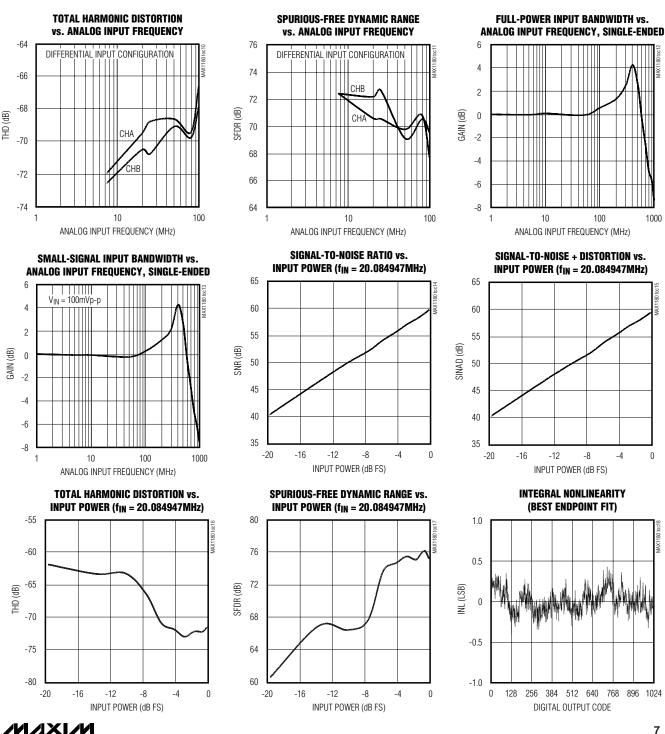

# Typical Operating Characteristics (continued)

$(V_{DD} = +3.3V, OV_{DD} = +2.5V, internal reference, differential input at -0.5dB FS, f_{CLK} = 105.0005678MHz, C_L \approx 10pF. T_A = +25^{\circ}C, T_A = +25^{\circ}C,$ unless otherwise noted.)

$(V_{DD} = +3.3V, OV_{DD} = +2.5V, internal reference, differential input at -0.5dB FS, f_{CLK} = 105.0005678MHz, C_L \approx 10pF. T_A = +25^{\circ}C, T_A = +25^{\circ}C,$

Typical Operating Characteristics (continued)

unless otherwise noted.)

#### **OFFSET ERROR vs. TEMPERATURE**, GAIN ERROR vs. TEMPERATURE, EXTERNAL REFERENCE (VREFIN = +2.048V) **DIFFERENTIAL NONLINEARITY** EXTERNAL REFERENCE (VREFIN = +2.048V) 0.50 1.0 1.0 0.5 0.25 0.5 OFFSET ERROR (%FS) CHB GAIN ERROR (%FS) CHA 0 DNL (LSB) 0 0 -0.5 CHB -0.25 -0.5 -10 -0.50 -1.5 -1.0 -40 85 0 128 256 384 512 640 768 896 1024 -15 10 35 60 -40 -15 10 35 60 85 TEMPERATURE (°C) TEMPERATURE (°C) DIGITAL OUTPUT CODE **ANALOG SUPPLY CURRENT ANALOG SUPPLY CURRENT** ANALOG POWER-DOWN CURRENT vs. ANALOG SUPPLY VOLTAGE vs. TEMPERATURE vs. ANALOG POWER SUPPLY 150 150 1.0 $\overline{OE} = PD = OV_{DD}$ 140 140 0.8 (W) 130 (W) 130 0.6 (Au) aavi 120 120 0.4 110 110 0.2 100 100 0 2.70 2.85 3.00 3.15 3.30 3.45 3.60 -40 -15 10 35 60 85 2 70 2.85 3.00 3.15 3.30 3.45 3 60 V<sub>DD</sub> (V) TEMPERATURE (°C) V<sub>DD</sub> (V) SFDR. SNR. THD. SINAD **INTERNAL REFERENCE VOLTAGE** vs. CLOCK DUTY CYCLE vs. ANALOG SUPPLY VOLTAGE 90 2.050 f<sub>IN</sub> = 20.08495MHz 80 2.046 SFDR, SNR, THD, SINAD (dB) SFDR THD () 2.042 100 2.038 70 SNR 60 SINAD 50 2.034 40 2.030 40 48 60 2.85 3.00 3.15 3.30 3.45 3.60 44 52 56 2.70 CLOCK DUTY CYCLE (%) V<sub>DD</sub> (V)

8

# **Typical Operating Characteristics (continued)**

$(V_{DD} = +3.3V, OV_{DD} = +2.5V, internal reference, differential input at -0.5dB FS, f_{CLK} = 105.0005678MHz, C_L \approx 10pF. T_A = +25^{\circ}C, unless otherwise noted.)$

# **MAX1180**

# **Pin Description**

| PIN              | NAME            | FUNCTION                                                                                                                     |

|------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| 1                | COM             | Common-Mode Voltage Input/Output. Bypass to GND with a $\ge 0.1 \mu$ F capacitor.                                            |

| 2, 6, 11, 14, 15 | V <sub>DD</sub> | Analog Supply Voltage. Bypass to GND with a capacitor combination of 2.2 $\mu$ F in parallel with 0.1 $\mu$ F.               |

| 3, 7, 10, 13, 16 | GND             | Analog Ground                                                                                                                |

| 4                | INA+            | Channel A Positive Analog Input. For single-ended operation, connect signal source to INA+.                                  |

| 5                | INA-            | Channel A Negative Analog Input. For single-ended operation, connect INA- to COM.                                            |

| 8                | INB-            | Channel B Negative Analog Input. For single-ended operation, connect INB- to COM.                                            |

| 9                | INB+            | Channel B Positive Analog Input. For single-ended operation, connect signal source to INB+.                                  |

| 12               | CLK             | Converter Clock Input                                                                                                        |

| 17               | T/B             | T/B selects the ADC digital output format.<br>High: Two's complement.<br>Low: Straight offset binary.                        |

| 18               | SLEEP           | Sleep Mode Input.<br>High: Deactivates the two ADCs, but leaves the reference bias circuit active.<br>Low: Normal operation. |

| 19               | PD              | Power-Down Input.<br>High: Power-down mode<br>Low: Normal operation                                                          |

| 20               | ŌĒ              | Output Enable Input.<br>High: Digital outputs disabled<br>Low: Digital outputs enabled                                       |

# Pin Description (continued)

| PIN    | NAME             | FUNCTION                                                                                                                                        |

|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 21     | D9B              | Three-State Digital Output, Bit 9 (MSB), Channel B                                                                                              |

| 22     | D8B              | Three-State Digital Output, Bit 8, Channel B                                                                                                    |

| 23     | D7B              | Three-State Digital Output, Bit 7, Channel B                                                                                                    |

| 24     | D6B              | Three-State Digital Output, Bit 6, Channel B                                                                                                    |

| 25     | D5B              | Three-State Digital Output, Bit 5, Channel B                                                                                                    |

| 26     | D4B              | Three-State Digital Output, Bit 4, Channel B                                                                                                    |

| 27     | D3B              | Three-State Digital Output, Bit 3, Channel B                                                                                                    |

| 28     | D2B              | Three-State Digital Output, Bit 2, Channel B                                                                                                    |

| 29     | D1B              | Three-State Digital Output, Bit 1, Channel B                                                                                                    |

| 30     | D0B              | Three-State Digital Output, Bit 0 (LSB), Channel B                                                                                              |

| 31, 34 | OGND             | Output Driver Ground                                                                                                                            |

| 32, 33 | OV <sub>DD</sub> | Output Driver Supply Voltage. Bypass to OGND with a capacitor combination of 2.2 $\mu$ F in parallel with 0.1 $\mu$ F.                          |

| 35     | D0A              | Three-State Digital Output, Bit 0 (LSB), Channel A                                                                                              |

| 36     | D1A              | Three-State Digital Output, Bit 1, Channel A                                                                                                    |

| 37     | D2A              | Three-State Digital Output, Bit 2, Channel A                                                                                                    |

| 38     | D3A              | Three-State Digital Output, Bit 3, Channel A                                                                                                    |

| 39     | D4A              | Three-State Digital Output, Bit 4, Channel A                                                                                                    |

| 40     | D5A              | Three-State Digital Output, Bit 5, Channel A                                                                                                    |

| 41     | D6A              | Three-State Digital Output, Bit 6, Channel A                                                                                                    |

| 42     | D7A              | Three-State Digital Output, Bit 7, Channel A                                                                                                    |

| 43     | D8A              | Three-State Digital Output, Bit 8, Channel A                                                                                                    |

| 44     | D9A              | Three-State Digital Output, Bit 9 (MSB), Channel A                                                                                              |

| 45     | REFOUT           | Internal Reference Voltage Output. May be connected to REFIN through a resistor or a resistor divider.                                          |

| 46     | REFIN            | Reference Input. $V_{REFIN} = 2 \times (V_{REFP} - V_{REFN})$ .<br>Bypass to GND with a >1nF capacitor.                                         |

| 47     | REFP             | Positive Reference Input/Output. Conversion range is $\pm$ (V <sub>REFP</sub> - V <sub>REFN</sub> ).<br>Bypass to GND with a > 0.1µF capacitor. |

| 48     | REFN             | Negative Reference Input/Output. Conversion range is $\pm$ (V <sub>REFP</sub> - V <sub>REFN</sub> ).<br>Bypass to GND with a > 0.1µF capacitor. |

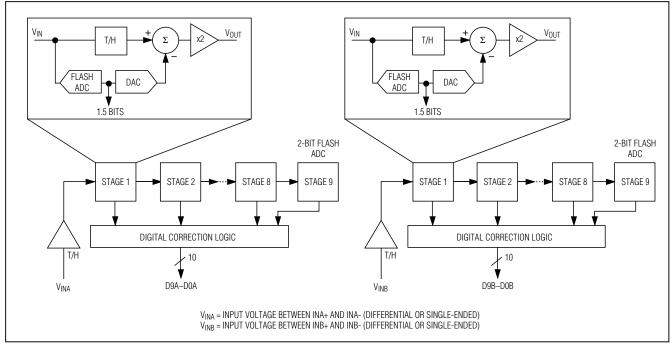

Figure 1. Pipelined Architecture—Stage Blocks

## **Detailed Description**

The MAX1180 uses a nine-stage, fully-differential pipelined architecture (Figure 1), that allows for high-speed conversion while minimizing power consumption. Samples taken at the inputs move progressively through the pipeline stages every half clock cycle. Counting the delay through the output latch, the clock-cycle latency is five clock cycles.

1.5-bit (two-comparator) flash ADCs convert the heldinput voltages into a digital code. The digital-to-analog converters (DACs) convert the digitized results back into analog voltages, which are then subtracted from the original held-input signals. The resulting error signals are then multiplied by two and the residues are passed along to the next pipeline stages where the process is repeated until the signals have been processed by all nine stages. Digital error correction compensates for ADC comparator offsets in each of these pipeline stages and ensures no missing codes.

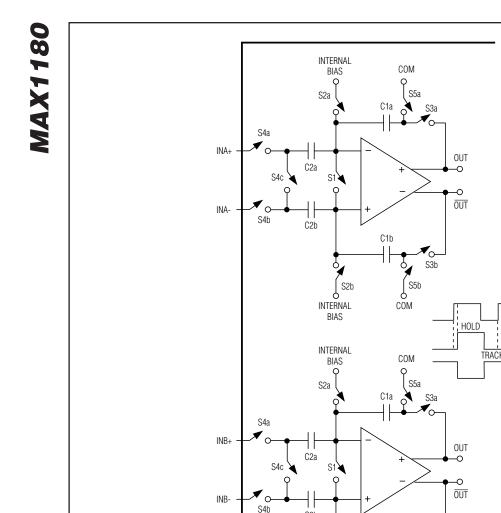

#### Input Track-and-Hold (T/H) Circuits

Figure 2 displays a simplified functional diagram of the input track-and-hold (T/H) circuits in both track-and-hold mode. In track mode, switches S1, S2a, S2b, S4a, S4b, S5a and S5b are closed. The fully-differential circuits sample the input signals onto the two capacitors

(C2a and C2b) through switches S4a and S4b. S2a and S2b set the common mode for the amplifier input, and open simultaneously with S1, sampling the input waveform. Switches S4a and S4b are then opened before switches S3a and S3b, connect capacitors C1a and C1b to the output of the amplifier, and switch S4c is closed. The resulting differential voltages are held on capacitors C2a and C2b. The amplifiers are used to charge capacitors C1a and C1b to the same values originally held on C2a and C2b. These values are then presented to the first-stage quantizers and isolate the pipelines from the fast-changing inputs. The wide input bandwidth T/H amplifiers allow the MAX1180 to trackand-sample/hold analog inputs of high frequencies (> Nyquist). Both ADC inputs (INA+, INB+, INA-, and INB-) can be driven either differentially or single-ended. Match the impedance of INA+ and INA-, as well as INB+ and INB-, and set the common-mode voltage to midsupply (V<sub>DD</sub>/2) for optimum performance.

#### Analog Inputs and Reference Configurations

The full-scale range of the MAX1180 is determined by the internally generated voltage difference between REFP (VDD/2 + VREFIN/4) and REFN (VDD/2 - VREFIN/4).The full-scale range for both on-chip

Figure 2. MAX1180 T/H Amplifiers

ADCs is adjustable through the REFIN pin, which is provided for this purpose.

C2b

S2b

INTERNAL

BIAS

C1b

S3b

6

COM

S5b

REFOUT, REFP, COM ( $V_{DD}/2$ ), and REFN are internally buffered low-impedance outputs.

The MAX1180 provides three modes of reference operation:

- Internal reference mode

- Buffered external reference mode

CLK

TRACK

INTERNAL

NONOVERLAPPING

CLOCK SIGNALS

/VI/IXI/VI

MAX1180

HOLD

• Unbuffered external reference mode

In the internal reference mode, connect the internal reference output REFOUT to REFIN through a resistor (e.g.,  $10k\Omega$ ) or resistor divider, if an application

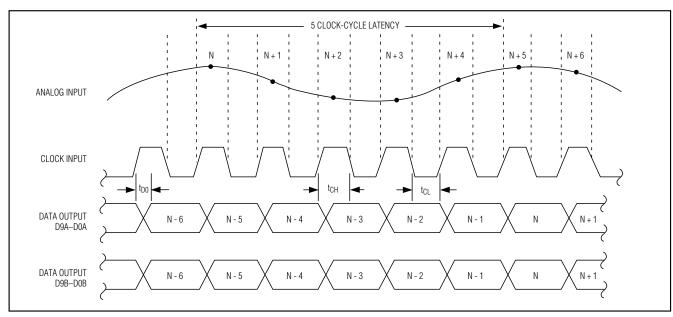

Figure 3. System Timing Diagram

| DIFFERENTIAL INPUT<br>VOLTAGE* | DIFFERENTIAL INPUT  | STRAIGHT OFFSET<br>BINARY<br>T/B = 0 | TWO'S COMPLEMENT<br>T/B = 1 |

|--------------------------------|---------------------|--------------------------------------|-----------------------------|

| V <sub>REF</sub> × 511/512     | +FULL SCALE - 1LSB  | 11 1111 1111                         | 01 1111 1111                |

| V <sub>REF</sub> × 1/512       | + 1 LSB             | 10 0000 0001                         | 00 0000 0001                |

| 0                              | Bipolar Zero        | 10 0000 0000                         | 00 0000 0000                |

| -V <sub>REF</sub> × 1/512      | - 1 LSB             | 01 1111 1111                         | 11 1111 1111                |

| -V <sub>REF</sub> × 511/512    | -FULL SCALE + 1 LSB | 00 0000 0001                         | 10 0000 0001                |

| -V <sub>REF</sub> × 512/512    | -FULL SCALE         | 00 0000 0000                         | 10 0000 0000                |

# Table 1. MAX1180 Output Codes For Differential Inputs

\*VREF = VREFP - VREFN

requires a reduced full-scale range. For stability and noise filtering purposes, bypass REFIN with a >10nF capacitor to GND. In internal reference mode, REFOUT, COM, REFP, and REFN become low-impedance outputs.

In the buffered external reference mode, adjust the reference voltage levels externally by applying a stable and accurate voltage at REFIN. In this mode, COM, REFP, and REFN become outputs. REFOUT may be left open or connected to REFIN through a >10k $\Omega$  resistor.

In the unbuffered external reference mode, connect REFIN to GND. This deactivates the on-chip reference buffers for REFP, COM, and REFN. With their buffers

shut down, these nodes become high impedance and may be driven through separate external reference sources.

## **Clock Input (CLK)**

The MAX1180's CLK input accepts CMOS-compatible clock signals. Since the interstage conversion of the device depends on the repeatability of the rising and falling edges of the external clock, use a clock with low jitter and fast rise and fall times (< 2ns). In particular, sampling occurs on the rising edge of the clock signal, requiring this edge to provide lowest possible jitter. Any significant aperture jitter would limit the SNR performance of the on-chip ADCs as follows:

**MAX1180**

$SNR_{dB} = 20 \times \log_{10} (1 / [2\pi \times f_{IN} \times t_{AJ}]),$

where  $f_{\text{IN}}$  represents the analog input frequency and  $t_{\text{AJ}}$  is the time of the aperture jitter.

Clock jitter is especially critical for undersampling applications. The clock input should always be considered as an analog input and routed away from any analog input or other digital signal lines.

The MAX1180 clock input operates with a voltage threshold set to  $V_{DD}/2$ . Clock inputs with a duty cycle other than 50%, must meet the specifications for high and low periods as stated in the *Electrical Characteristics*.

## **System Timing Requirements**

Figure 3 depicts the relationship between the clock input, analog input, and data output. The MAX1180 samples at the rising edge of the input clock. Output data for channels A and B is valid on the next rising edge of the input clock. The output data has an internal latency of five clock cycles. Figure 4 also determines the relationship between the input clock parameters and the valid output data on channels A and B.

## Digital Output Data, Output Data Format Selection (T/B), Output Enable (OE)

All digital outputs, D0A-D9A (Channel A) and D0B-D9B (Channel B), are TTL/CMOS logic-compatible. There is a five clock cycle latency between any particular sample and its corresponding output data. The output coding can be chosen to be either straight offset binary or two's complement (Table 1) controlled by a single pin (T/B). Pull T/B low to select offset binary and high to activate two's complement output coding. The capacitive load on the digital outputs D0A–D9A and D0B–D9B should be kept as low as possible (<15pF), to avoid large digital currents that could feed back into the analog portion of the MAX1180, thereby degrading its dynamic performance. Using buffers on the digital outputs of the ADCs can further isolate the digital outputs from heavy capacitive loads. To further improve the dynamic performance of the MAX1180 small-series resistors (e.g.,  $100\Omega$ ), add to the digital output paths, close to the MAX1180.

Figure 4 displays the timing relationship between output enable and data output valid, as well as power-down/wake-up and data output valid.

## Power-Down (PD) and Sleep (SLEEP) Modes

The MAX1180 offers two power-save modes, sleep and full power-down mode. In sleep mode (SLEEP = 1), only the reference bias circuit is active (both ADCs are

Figure 4. Output Timing Diagram

disabled) and current consumption is reduced to 2.8mA.

To enter full power-down mode, pull PD high. With  $\overline{\text{OE}}$  simultaneously low, all outputs are latched at the last value prior to the power-down. Pulling  $\overline{\text{OE}}$  high, forces the digital outputs into a high-impedance state.

# **Applications Information**

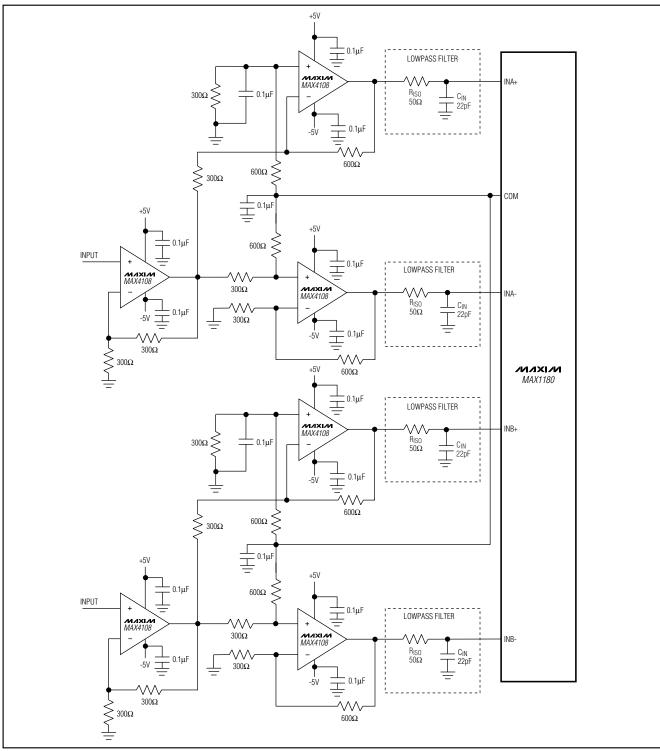

Figure 5 depicts a typical application circuit containing two single-ended to differential converters. The internal reference provides a V<sub>DD</sub>/2 output voltage for level-shifting purposes. The input is buffered and then split to a voltage follower and inverter. One lowpass filter per ADC suppresses some of the wideband noise associated with high-speed operational amplifiers. The user may select the RISO and C<sub>IN</sub> values to optimize the filter performance to suit a particular application. For the application in Figure 5, a RISO of 50 $\Omega$  is placed before the capacitive load to prevent ringing and oscillation. The 22pF C<sub>IN</sub> capacitor acts as a small bypassing capacitor.

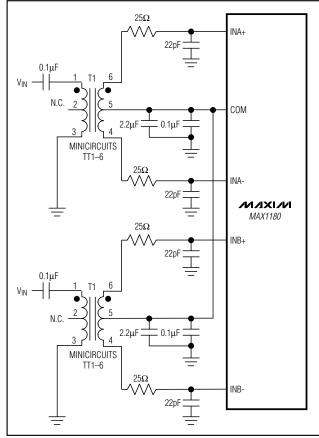

## **Using Transformer Coupling**

An RF transformer (Figure 6) provides an excellent solution to convert a single-ended source signal to a fully-differential signal, required by the MAX1180 for optimum performance. Connecting the center tap of the transformer to COM provides a VDD/2 DC level shift to the input. Although a 1:1 transformer is shown, a step-up transformer may be selected to reduce the drive requirements. A reduced signal swing from the input driver, such as an op amp, may also improve the overall distortion.

In general, the MAX1180 provides better SFDR and THD with fully-differential input signals, than a singleended drive, especially for high input frequencies. In differential input mode, even-order harmonics are lower as both inputs (INA+, INA- and/or INB+, INB-) are bal-

Figure 5. Typical Application for Single-Ended to Differential Conversion

Figure 6. Transformer-Coupled Input Drive

anced, and each of the ADC inputs only require half the signal swing compared to single-ended mode.

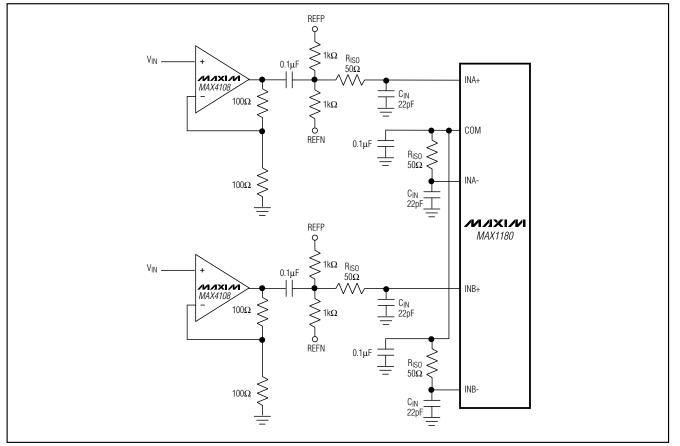

## Single-Ended AC-Coupled Input Signal

Figure 7 shows an AC-coupled, single-ended application. Amplifiers, like the MAX4108, provide high-speed, high bandwidth, low-noise, and low distortion to maintain the integrity of the input signal.

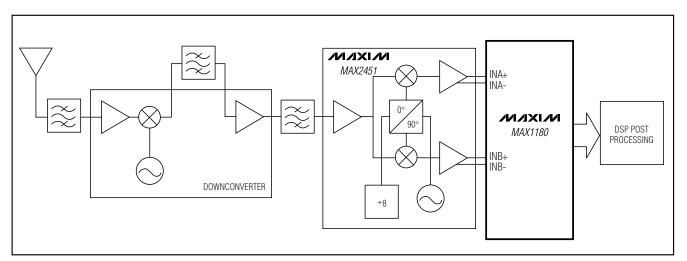

**Typical QAM Demodulation Application** The most frequently used modulation technique for digital communications application is the Quadrature Amplitude Modulation (QAM). QAMs are typically found in spread-spectrum based systems. A QAM signal represents a carrier frequency modulated in both amplitude and phase. At the transmitter, modulating the baseband signal with quadrature outputs, a local oscil-

lator followed by subsequent up-conversion can generate the QAM signal. The result is an in-phase (I) and a quadrature (Q) carrier component, where the Q component is 90 degrees phase-shifted with respect to the inphase component. At the receiver, the QAM signal is divided down into its I and Q components, essentially representing the modulation process reversed. Figure 8 displays the demodulation process performed in the analog domain, using the dual-matched, +3V, 10-bit ADCs, MAX1180 and the MAX2451 guadrature demodulators, to recover and digitize the I and Q baseband signals. Before being digitized by the MAX1180, the mixed-down signal components may be filtered by matched analog filters, such as Nyquist or Pulse-Shaping filters which remove any unwanted images from the mixing process, enhances the overall signalto-noise (SNR) performance, and minimizes intersymbol interference.

# Grounding, Bypassing, \_\_\_\_\_and Board Layout

The MAX1180 requires high-speed board layout design techniques. Locate all bypass capacitors as close to the device as possible, preferably on the same side as the ADC, using surface-mount devices for minimum inductance. Bypass VDD, REFP, REFN, and COM with two parallel 0.1µF ceramic capacitors and a 2.2µF bipolar capacitor to GND. Follow the same rules to bypass the digital supply (OV<sub>DD</sub>) to OGND. Multilayer boards with separate ground and power planes, produce the highest level of signal integrity. Consider the use of a split ground plane arranged to match the physical location of the analog ground (GND) and the digital output driver ground (OGND) on the ADCs package. The two ground planes should be joined at a single point, such that the noisy digital ground currents do not interfere with the analog ground plane. The ideal location of this connection can be determined experimentally at a point along the gap between the two ground planes, which produces optimum results. Make this connection with a low-value, surface-mount resistor  $(1\Omega \text{ to } 5\Omega)$ , a ferrite bead, or a direct short. Alternatively, all ground pins could share the same ground plane, if the ground plane is sufficiently isolated from any noisy, digital systems ground plane (e.g., downstream output buffer or DSP ground plane). Route high-speed digital signal traces away from the sensitive analog traces of either channel. Make sure to isolate the analog input lines to each respective converter to

Figure 7. Using an Op Amp for Single-Ended, AC-Coupled Input Drive

Figure 8. Typical QAM Application, Using the MAX1180

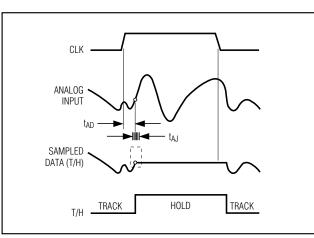

Figure 9. T/H Aperture Timing

MAX1180

minimize channel-to-channel crosstalk. Keep all signal lines short and free of 90 degree turns.

# **Static Parameter Definitions**

#### **Integral Nonlinearity (INL)**

Integral nonlinearity is the deviation of the values on an actual transfer function from a straight line. This straight line can be either a best straight-line fit or a line drawn between the endpoints of the transfer function, once offset and gain errors have been nullified. The static linearity parameters for the MAX1180 are measured using the best straight-line fit method.

#### **Differential Nonlinearity (DNL)**

Differential nonlinearity is the difference between an actual step-width and the ideal value of 1LSB. A DNL error specification of less than 1LSB guarantees no missing codes and a monotonic transfer function.

# **Dynamic Parameter Definitions**

#### **Aperture Jitter**

Figure 9 depicts the aperture jitter  $(t_{AJ})$ , which is the sample-to-sample variation in the aperture delay.

#### **Aperture Delay**

Aperture delay (t<sub>AD</sub>) is the time defined between the falling edge of the sampling clock and the instant when an actual sample is taken (Figure 9).

## Signal-to-Noise Ratio (SNR)

For a waveform perfectly reconstructed from digital samples, the theoretical maximum SNR is the ratio of the full-scale analog input (RMS value) to the RMS quantization error (residual error).

The ideal, theoretical minimum analog-to-digital noise is caused by quantization error only and results directly from the ADCs resolution (N-Bits):

$$SNR_{dB[max]} = 6.02_{dB} \times N + 1.76_{dB}$$

In reality, there are other noise sources besides quantization noise; thermal noise, reference noise, clock jitter, etc. SNR is computed by taking the ratio of the RMS signal to the RMS noise, which includes all spectral components minus the fundamental, the first five harmonics, and the DC offset.

#### Signal-to-Noise Plus Distortion (SINAD)

SINAD is computed by taking the ratio of the RMS signal to all spectral components minus the fundamental and the DC offset.

#### **Effective Number of Bits (ENOB)**

ENOB specifies the dynamic performance of an ADC at a specific input frequency and sampling rate. An ideal ADC's error consists of quantization noise only. ENOB is computed from:

$$ENOB = \frac{SINAD_{dB} - 1.76_{dB}}{6.02_{dB}}$$

#### **Total Harmonic Distortion (THD)**

THD is typically the ratio of the RMS sum of the first four harmonics of the input signal to the fundamental itself. This is expressed as:

THD = 20 × log<sub>10</sub>

$$\left(\frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2}}{V_1}\right)$$

where  $V_1$  is the fundamental amplitude, and  $V_2$  through  $V_5$  are the amplitudes of the 2nd- through 5th-order harmonics.

#### **Spurious-Free Dynamic Range (SFDR)** SFDR is the ratio expressed in decibels of the RMS amplitude of the fundamental (maximum signal component) to the RMS value of the next largest spurious component, excluding DC offset.

#### Intermodulation Distortion (IMD)

The two-tone IMD is the ratio expressed in decibels of either input tone to the worst 3rd-order (or higher) intermodulation products. The individual input tone levels are at -6.5dB full scale and their envelope is at -0.5dB full scale.

## \_Chip Information

TRANSISTOR COUNT: 10,811 PROCESS: CMOS

# **Functional Diagram**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2001 Maxim Integrated Products

20

Printed USA

MAXIM is a registered trademark of Maxim Integrated Products.

21-0065

E 2/2